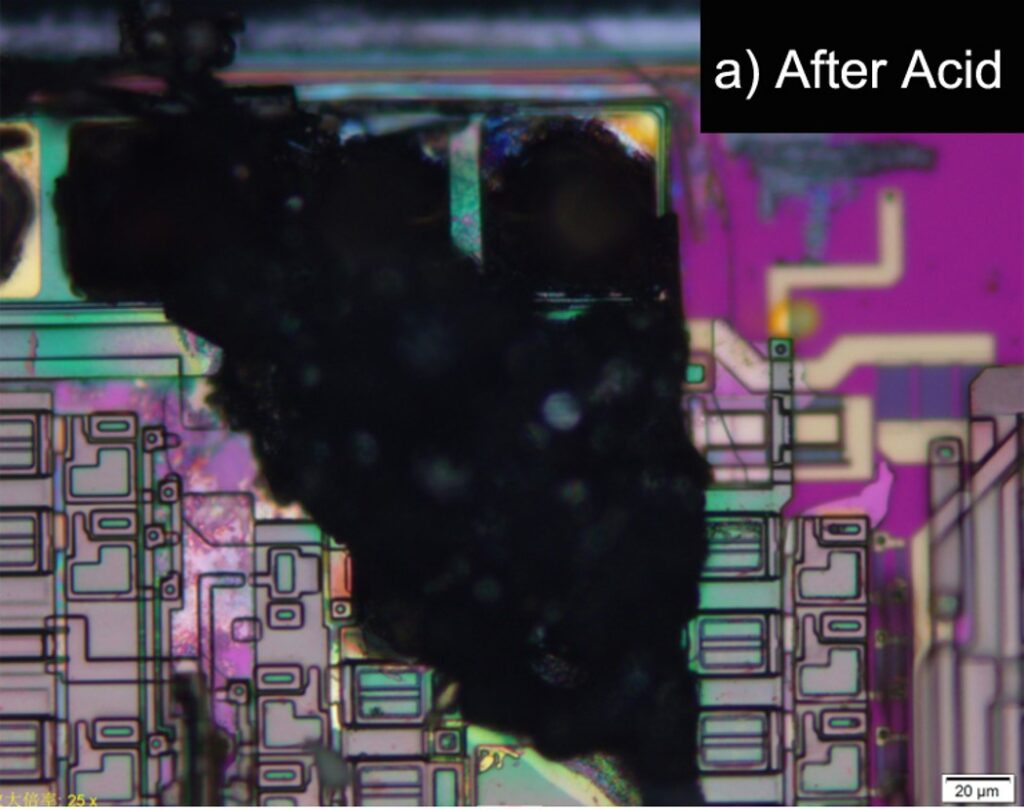

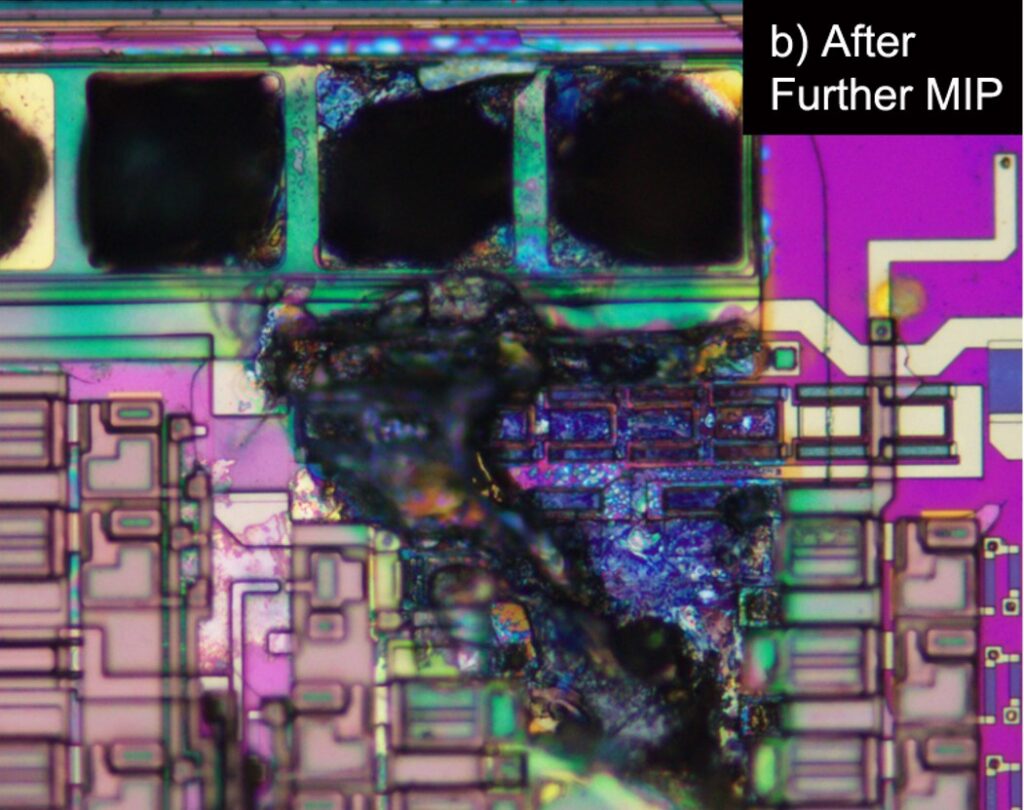

Electrical overstress (EOS) occurs when the voltage, current, or power in the device exceeds some maximal limit, inducing thermal damage in the device. This is one of the most common types of electrical failures, found in all stages of the IC device life cycle. Determining the root cause of EOS is integral to prevent future failures, but due to the thermal stress, the failure site is often covered by hardened mold compound. MIP decapsulation has been shown to fully remove the carbonized mold compound and expose the failure site, where other decapsulation methods fall short.

Limitations of conventional decapsulation methods

Conventional methods of decapsulating like halogen containing plasma and acid decapsulation cannot achieve the same level of results. Halogen containing plasma will etch into the passivation layer and die, complicating root cause analysis. Conventional acid decapsulation often cannot remove the hardened mold compound, requiring failure analysis to be done with additional processing steps through backside milling.

Where MIP stands out

MIP’s halogen free plasma formulation is highly selective, and does not etch the passivation layer. This allows for the carbonized mold compound to be fully removed while leaving the passivation layer and die circuitry intact. MIP’s plasma formulation does not leave behind any artifacts, ensuring the failure site is both fully exposed, and in its original state. Further failure analysis on the circuitry is possible, allowing for the root cause of the EOS to be determined.

Interested in learning more about MIP’s selectivity in EOS exposure? Download the IPFA 2017 detailing this case study here:

Unique Failure Analysis Capabilities Enabled by the MIP Decapsulation Technique

Ready to take your EOS failure analysis to the next level in terms of reliability and consistency?